# **Embedded Single Board Computer**

# GESBC-9G20 User's Manual

# **Table of Contents**

| Chapter I – Introducing the GESBC-9G20 Single Board Computer | 4  |

|--------------------------------------------------------------|----|

| GESBC-9G20 Overview                                          |    |

| Advanced Features                                            | 4  |

| AT91SAM9G20                                                  | 5  |

| SDRAM                                                        | 5  |

| FLASH                                                        | 5  |

| USB                                                          | 5  |

| UART 1                                                       |    |

| UART 2                                                       | 5  |

| DEBUG Port                                                   | 5  |

| Ethernet                                                     |    |

| Chapter 2 – Getting Started                                  | 7  |

| Assembly and Connections                                     | 7  |

| Operation                                                    | 7  |

| Configurations                                               |    |

| Chapter 3 – GESBC-9G20 Function Blocks                       | 10 |

| AT91SAM9G20                                                  | 10 |

| SDRAM                                                        |    |

| FLASH                                                        | 10 |

| USB                                                          |    |

| RS-232 Port 0, 1, and 2                                      | 11 |

| RS-485                                                       | 12 |

| I2C Bus                                                      | 12 |

| Ethernet                                                     | 12 |

| USB Port                                                     |    |

| SPI Bus, On-chip A/D and GPIO                                | 13 |

| RTC                                                          | 14 |

| JTAG                                                         | 14 |

| Power Requirement                                            | 15 |

| Chapter 4 – Software Description                             | 16 |

| Overview                                                     |    |

| Data Storage on GESBC-9G20                                   | 16 |

| GESBC-9G20 Linux Code                                        |    |

| U-boot                                                       |    |

| U-boot Booting Linux                                         |    |

| Loading Linux Kernel and root File System                    |    |

| Chapter 5 – Development Tools                                |    |

| Overview                                                     |    |

| Linux Development Tool Chain                                 |    |

| Chapter 6 – Troubleshooting                                  |    |

# **List of Tables**

| Table 1 System Configuration                                              |       |

|---------------------------------------------------------------------------|-------|

| Table 2 Debug UART Port P0 Connector on GESBC-9G20Error! Bookmark not det | fined |

| Table 3 UART Port P0 Connector on GESBC-9G20B                             | 11    |

| Table 4 UART Port P1 Connector                                            | 11    |

| Table 5 UART3 Port 2 Connector                                            |       |

| Table 6 RS-485 Port J8                                                    | 12    |

| Table 7 J9 I2C bus                                                        | 12    |

| Table 8 J17 USB Device Port                                               | 13    |

| Table 9 J16 I/O Expansion                                                 | 13    |

| Table 10 J20 JTAG Connector                                               |       |

| Table 11 J1 Power Supply Connector                                        | 15    |

| Table 12 NAND FLASH Storage Map                                           |       |

20-Jun-09

# Chapter 1 – Introducing the GESBC-9G20 Single Board Computer

#### **GESBC-9G20 Overview**

The GESBC-9G20 is a low cost compact sized single board computer based on Atmel AT91SAM9G20 processor. With a large peripheral set targeted to a variety of applications, the GESBC-9G20 is well suited for industrial controls, digital media servers, audio jukeboxes, thin clients, set-top boxes, point-of-sale terminals, biometric security systems, and GPS devices.

#### **Advanced Features**

The heart of the GESBC-9G20 is the AT91SAM9G20 which is the one in a series of ARM926EJ-S-based processors. The AT91SAM9G20 microcontroller features DSP Instruction Extensions, ARM Jazelle® Technology for Java® Acceleration. It has separate 8 Kbyte instruction and data caches with write buffer. The ARM926EJ-S on the AT91SAM9G20 functions with a maximum operating clock rate of 400MHz and a power usage between 20mW and 80mW (dependent upon clock speed). The ARM core operates from a 1V supply while the I/O operates at 3.3V. The low power consumption makes it an idea platform for battery operated applications.

The list below summarizes the features of the GESBC-9G20.

- 400MHz Processor Core ARM926EJ-S with MMU

- 64~ 128 MB SDRAM

- 256MB ~ 1GB NAND FLASH

- 1 10/100 Mbps Ethernet port

- 4 channel 10-bit Analog-to-Digital Converter (ADC

- 3 RS-232 Universal Asynchronous Receiver / Transmitters (UARTs)

- 1 RS-485 Port

- 2 USB Host Port

- 1 USB Device Port

- Real-Time Clock with battery backup

- Hardware Debug Interface

- SD/MMC Socket

- 1 I2C Port

- 1 SPI Port

Figure 1 below shows a picture of the GESBC-9G20 Single Board Computer.

Figure 1. GESBC-9G20 Single Board Computer

#### AT91SAM9G20

The GESBC-9G20 is shipped with the Atmel AT91SAM9G20 processor. For more information regarding the AT91SAM9G20 processor please see the AT91SAM9G20 datasheet.

#### **SDRAM**

The GESBC-9G20 is shipped with 64MBytes of SDRAM.

#### **FLASH**

The GESBC-9G20 is shipped with 256MB NAND FLASH.

#### **USB**

The GESBC-9G20 is shipped with two USB host ports.

#### **UART 1**

The GESBC-9G20 is shipped with a full RS-232 interface with modem control signals

#### **UART 2**

The GESBC-9G20 is shipped with the 3 wire UART 2 interface.

#### **DEBUG Port**

The GESBC-9G20 is shipped with the 3 wire serial debug port.

## **Ethernet**

The GESBC-9G20 is shipped with a complete physical and MAC subsystem that is compliant with the ISO/TEC 802.3 topology for a single shared medium with several stations. The AT91SAM9G20 supports 1/10/100 Mbps transfer rates and interfaces to industry standard physical layer devices.

# **Chapter 2 – Getting Started**

This chapter describes the GESBC-9G20 working environment and familiarizes the user with its components and functionality. This chapter contains the following sections:

- Assembly and Connections

- Describes how to assemble and connect components to the GESBC-9G20 Single Board Computer

- Operation

- o Describes how to operate the GESBC-9G20 Single Board Computer

## **Assembly and Connections**

In order to use the GESBC-9G20 the user must first assemble and connect the peripherals to the GESBC-9G20, as described in the following procedure.

- 1. Place the GESBC-9G20 on a static free surface.

- 2. Make sure all of the jumpers are in the factory default position. The unit is shipped in a factory default configuration. If the user is uncertain that the GESBC-9G20 has the jumpers in the factory default configuration, please see the next section regarding board configuration.

- 3. Connect 5V regulated power supply to the board.

- 4. Connect null modem serial cable between GESBC-9G20 debug port and PC/terminal serial port.

- 5. Launch a terminal emulator, such as HyperTerminal, or minicom, on the PC configured to connect to the serial port of the GESBC-9G20. Configure the serial port with the following parameters: 115200 bits per second, 8 data bits, no parity, 1 stop bit, no flow control.

- 6. Connect the board to a local area network (optional)

## Operation

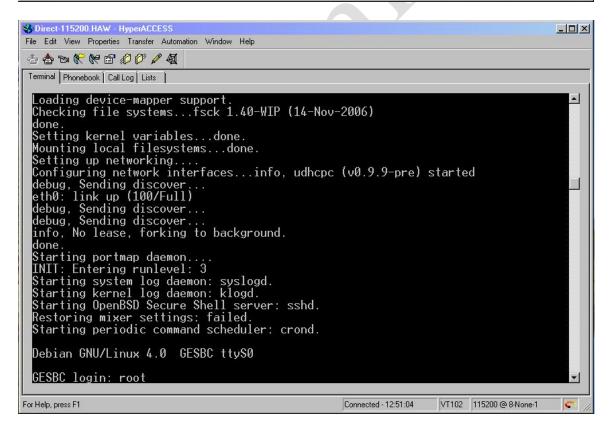

A few seconds after applying power to the GESBC-9G20, debug information will be displayed on the terminal program. The following figures show what this should look like.

```

Direct-115200.HAW - HyperACCESS

_ 🗆 ×

File Edit View Properties Transfer Automation Window Help

Terminal Phonebook Call Log Lists

RomB00T

U-Boot 1.3.3 (Jul 19 2008 - 15:50:33)

DRAM: 64 MB

NAND: 128 MiB

DataFlash:AT45DB642

Nb pages: 8192

Page Size: 1056

Size= 8650752 bytes

Logical address: 0xD0000000

Area 0: D0000000 to D00041FF (RO) Bootstrap

Area 1: D0004200 to D00083FF Enviro

Area 2: D0008400 to D0041FFF (RO) U-Boot

Area 3: D0042000 to D0251FFF Kernel

Area 4: D0252000 to D083FFFF FS

Environment

*** Warning – bad CRC or NAND, using default environment

In:

serial

Out:

serial

serial

macb0

Starting autonegotiation.

Err:

Net:

VT102 115200 @ 8-None-1

Connected - 12:47:16

For Help, press F1

```

Please see

Chapter 4 – Software Description for more details regarding the software functionality.

# Configurations

Jumpers are used to configure the GESBC-9G20 to operate in different mode. The following table lists all the settings for each jumper.

**Table 1 System Configuration**

| Jumper | Description                                            |

|--------|--------------------------------------------------------|

| J7     | Boot mode:                                             |

|        | connect pin 1 and 2 – external memory boot on NCS0     |

|        | open pin 1 and 2 – internal ROM boot (NAND FLASH boot) |

| S1     | PA31 port input for boot strap code boot mode          |

|        | open – normal ROM boot sequence                        |

|        | close – ROM debug mode                                 |

| BP1    | System reset switch header                             |

# **Chapter 3 – GESBC-9G20 Function Blocks**

#### AT91SAM9G20

The GESBC-9G20 Single Board Computer uses the Atmel AT91SAM9G20 as the core processor on this development board. The top-level features of AT91SAM9G20 processor are the following:

- ARM926EJ-S RISC Core Processor

- 400 MHz / 400 MIPS Performance

- 32Kbyte Instruction Cache

- 32Kbyte Data Cache

- Linux and Windows CE enabled MMU

- 100 MHz System Bus

- 32 bit SDRAM Interface

- 32 bit SRAM / FLASH / ROM Interface

- Serial EEPROM Interface

- 10 / 100 Mbps Ethernet MAC

- 6 UART

- Two-port USB Host

- 4 channel 10 bit ADC

- 2 SPI Port

- Serial Audio Interface

- JTAG Interface

More detailed information regarding the AT91SAM9G20 processor can be found at www.atmel.com.

#### **SDRAM**

The AT91SAM9G20 features a unified memory address model where all memory devices are accessed over a common address and data bus. The GESBC-9G20 supports up to 128MB SDRAM.

#### **FLASH**

The GESBC-9G20 is shipped with 256 Mbytes of NAND FLASH memory. The GESBC-9G20 can be also ordered with optional 512MB ~ 1GB NAND FLASH.

#### **USB**

The GESBC-9G20 Single Board Computer provides two USB host connections. The AT91SAM9G20 USB host controller is configured for two root hub ports and features an integrated transceiver for each port. The AT91SAM9G20 integrates two USB 2.0 Full Speed host ports. These ports are fully compliant to the OHCI USB 2.0 Full Speed specification (12 Mbps). The controller complies with the OHCI specification for USB Revision 1.1. The USB ports are brought out by a standard double deck USB type A connector.

The GESBC-9G20 Single Board Computer provides one USB device port. The USB Device Port (UDP) is compliant with the Universal Serial Bus (USB) V2.0 full-speed device specification.

#### RS-232 Port 0, 1, and 2

The GESBC-9G20 Single Board Computer is shipped with two 3-wire RS-232 UART interface, and one 9 wire RS-232 UART interface.

The port 0 is the debug USART port of the AT91SAM9G20. The P0 connector is the 3 pin header on GESBC-9G20. The signal designation is listed in the following tables.

Table 2 UART Port P0 Connector on GESBC-9G20

| Pin Number | Signal Name |

|------------|-------------|

| 1          | RX          |

| 2          | TX          |

| 3          | GND         |

The serial port 1 is the USART 0 on the AT91SAM9G20 processor. It is provided via the DB-9 connector on GESBC-9G20. The UART P1 provides full modem control and hardware handshake signals.

**Table 3 UART Port P1 Connector**

| Pin Number | Signal Name | Pin Number | Signal Name |

|------------|-------------|------------|-------------|

| 1          | DCD         | 2          | RX          |

| 3          | TX          | 4          | DTR         |

| 5          | GND         | 6          | DSR         |

| 7          | RTS         | 8          | CTS         |

| 9          | RI          | 10         | NC/NA       |

The port 2 is the USART 1 of the AT91SAM9G20. It is provided via a 3 pin header P2.

**Table 4 UART3 Port 2 Connector**

| Pin Number | Signal Name |

|------------|-------------|

| 1          | RX          |

| 2          | TX          |

| 3          | GND         |

#### **RS-485**

The GESBC-9G20 Single Board Computer provides one half duplex RS-485 port. The RS-485 port is connected to USART3 with RTS signal for RS-485 driver direction control. The RS-485 signal is provided via a 1x3 2.54mm spacing header J8. J6 enables the on-board 120 ohm termination resistor.

Table 5 RS-485 Port J8

| Pin Number | Signal Name |

|------------|-------------|

| 1          | A           |

| 2          | В           |

| 3          | GND         |

The RTC3 is connected to the RS-485 driver chip for data direction control. The normal setting of RTS signal is normally low. For RS-485 mode the RTS signal must set to normally high. The user program must set the RTS mode before RS-485 port can be used.

#### **I2C Bus**

The GESBC-9G20 Single Board Computer provides one I2C bus interface via a 1x3 2.54mm spacing header J9.

Table 6 J9 I2C bus

| Pin Number | Signal Name |

|------------|-------------|

| 1          | SDA         |

| 2          | SCL         |

| 3          | GND         |

#### **Ethernet**

The GESBC-9G20 Single Board Computer is shipped with support for a complete Ethernet interface. The AT91SAM9G20 contains a MAC subsystem that is compliant with the ISO/TEC 802.3 topology for a single shared medium with several stations. The Media Access Controller (MAC) within the AT91SAM9G20 supports 1/10/100 Mbps transfer rates and interfaces to industry standard physical layer devices. The GESBC-9G20 is shipped with the DM9161A 100Base-X / 10Base-T Transceiver device which, along with a RJ45 connector, provides the physical layer interface.

#### **USB Port**

The GESBC-9G20 Single Board Computer is shipped with 2 USB host port on standard USB type-A double deck connector.

The GESBC-9G20 Single Board Computer is shipped with one USB device port J17. The USB device port signal assignment is listed in the following table.

**Table 7 J17 USB Device Port**

| Pin Number | Signal Name    |

|------------|----------------|

| 1          | USB connection |

| 2          | DM             |

| 3          | DP             |

| 4          | GROUND         |

| 5          | GROUND         |

## SPI Bus, On-chip A/D and GPIO

The AT91SAM9G20 contains very rich set of peripherals that are multiplex into 2 groups, Peripheral A and Peripheral B, with individually programmable pins. The SPI bus, A/D and GPIO are provided together with other functions on the I/O expansion port. The I/O expansion port is a 2x25 2.54mm spacing header. The following table lists signals available on the I/O expansion connector with their corresponding multiplexed functions and default usage on the GESBC-9G20 Single Board Computer.

Table 8 J16 I/O Expansion

| Pin | I/O Line | _          | Peripheral B | Comments | Function      |

|-----|----------|------------|--------------|----------|---------------|

| 1   |          |            |              |          | +3.3V         |

| 2   |          | _          |              |          | +3.3V         |

| 3   | PB0      | SPI1_MISO  | TIOA3        |          |               |

| 4   | PB1      | SPI1_MOSI  | TIOB3        |          |               |

| 5   | PB2      | SPI1_SPCK  | TIOA4        |          |               |

| 6   | PB3      | SPI1_NPCS0 | TIOA5        |          |               |

| 7   | PB4      | TXD0       |              |          | RS-232 Port 1 |

| 8   | PB5      | RXD0       |              |          | RS-232 Port 1 |

| 9   | PB6      | TXD1       | TCLK1        |          | RS-232 Port 2 |

| 10  | PB7      | RXD1       | TCKL2        |          | RS-232 Port 2 |

| 11  | PB8      | TXD2       |              |          |               |

| 12  | PB9      | RXD2       |              |          |               |

| 13  | PB10     | TXD3       | ISI_D8       |          | RS-485 Port   |

| 14  | PB11     | RXD3       | ISI_D9       |          | RS-485 Port   |

| 15  | PB12     | TXD5       | ISI_D10      |          |               |

| 16  | PB13     | RXD5       | ISI_D11      |          |               |

| 17  | PB14     | DRXD       |              |          | RS-232 Port 0 |

| 18  | PB15     | DTXD       |              |          | RS-232 Port 0 |

| 19  | PB16     | TK0        | TCLK3        |          |               |

| 20  | PB17     | TF0        | TCLK4        |          |               |

| 21  | PB18     | TD0        | TIOB4        |          |               |

| 22 | PB19 | RD0        | TIOB5       |               |

|----|------|------------|-------------|---------------|

| 23 | PB20 | RK0        | ISI_D0      |               |

| 24 | PB21 | RF0        | ISI_D1      |               |

| 25 | PB22 | DSR0       | ISI_D2      | RS-232 Port 1 |

| 26 | PB23 | DCD0       | ISI_D3      | RS-232 Port 1 |

| 27 | PB24 | RTR0       | ISI_D4      | RS-232 Port 1 |

| 28 | PB25 | RI0        | ISI_D5      | RS-232 Port 1 |

| 29 | PB26 | RTC0       | ISI_D6      | RS-232 Port 1 |

| 30 | PB27 | CTS0       | ISI_D7      | RS-232 Port 1 |

| 31 | PB28 | RTS1       | ISI_PCK     |               |

| 32 | PB29 | CTS1       | ISI_VSYNC   |               |

| 33 | PB30 | PCK0       | ISI_HSYNC   |               |

| 34 | PB31 | PCK1       | ISIMCK      |               |

| 35 |      |            |             | GND           |

| 36 |      |            |             | GND           |

| 37 | PC0  | AD0        | SCK3        | 0/70          |

| 38 | PC1  | AD1        | PCK0        |               |

| 39 | PC2  | AD2        | PCK1        |               |

| 40 | PC3  | AD3        | SPI1_NPCS3  | , /           |

| 41 | PC4  | A23        | SPI1_NPCS2  |               |

| 42 | PC5  | A24        | SPI1_NPCS1_ |               |

| 43 | PC6  | TIOB2      | CFCE1       |               |

| 44 | PC7  | TIOB3      | CFCE2       |               |

| 45 | PC8  | NCS4/CFCS0 | RTS3        | RS-485        |

| 46 | PC9  | NCS5/CFCS1 | TIOB0       |               |

| 47 | PC10 | A25/CFRNW  | CTS3        |               |

| 48 | PC11 | NCS2       | SPINPCS1    |               |

| 49 |      |            |             | GND           |

| 50 |      |            |             | GND           |

For more detailed information on multiplexed peripherals please see AT91SAM9G20 data sheet.

#### **RTC**

The GESBC-9G20 uses the AT91SAM9G20 on-chip RTC with battery hook-up to provide accurate time keeping. The on-board battery holder accepts CR1225/CR1220 coin cell batteries.

#### **JTAG**

The GESBC-9G20 Single Board Computer is shipped with a 10 pin connector that provides JTAG debug signals for the CPU. The JTAG provides the user with the ability to debug system level programs. The signal designation is listed in the following table.

#### **Table 9 J20 JTAG Connector**

| Pin Number Signal Name Pin Number Signal Name |  |

|-----------------------------------------------|--|

|-----------------------------------------------|--|

| 1 | 3.3V  | 2  | 3.3V |

|---|-------|----|------|

| 3 | NTRST | 4  | TDI  |

| 5 | TMS   | 6  | TCK  |

| 7 | RTCK  | 8  | TDO  |

| 9 | GND   | 10 | GND  |

# **Power Requirement**

The GESBC-9G20 Single Board Computer requires regulated 5V DC. The power supply should have minimum 300mA capacity.

**Table 10 J1 Power Supply Connector**

| Pin Number | Signal Name |

|------------|-------------|

| 1          | 5V DC       |

| 2          | GND         |

# **Chapter 4 – Software Description**

#### Overview

This chapter provides information regarding the software that is shipped with the GESBC-9G20 Board. The software included with the board is U-boot boot loader, Linux kernel 2.6.25, and Debian distribution style compact root file system. The applications included provide access to all hardware functions on the GESBC-9G20 board.

## **Data Storage on GESBC-9G20**

The default configuration of the GESBC-9G20 Single Board Computer uses on board NAND FLASH for all data storage requirements, including boot strap code, boot loader, Linux kernel, and Linux file system.

The following table is the factory default storage map on the NAND FLASH.

**Table 11 NAND FLASH Storage Map**

| Start Address | Size     | Usage                                      |

|---------------|----------|--------------------------------------------|

| 0x00000000    | 0x20000  | Boot strap code                            |

| 0x00020000    | 0x40000  | U-boot                                     |

| 0x00060000    | 0x40000  | U-boot primary environment storage range   |

| 0x000A0000    | 0x40000  | U-boot secondary environment storage range |

| 0x00100000    | 0x300000 | Linux kernel                               |

| 0x00400000    |          | Root file system                           |

#### **GESBC-9G20 Linux Code**

The GESBC-9G20 is shipped with Linux 2.6.27 kernel pre-installed. This software is programmed into the system FLASH located on the board prior to shipment. The Linux kernel is configured with all the device drivers included for the GESBC-9G20 board.

#### **U-boot**

U-boot provides a simple interface for loading operating systems and applications onto the GESBC-9G20 board. U-Boot uses a serial console for its input and output. The default serial port setting is 115200,8,N,1. It also supports the built-in Ethernet port and general flash programming.

The board is shipped with U-boot pre-installed. Please refer to U-boot user's manual regarding detailed information of U-boot.

# **U-boot Booting Linux**

The following shows the default U-boot setup for booting Linux.

```

U-Boot> printenv

bootargs=console=ttyS0,115200 root=/dev/mtdblock2 rw rootfstype

= jffs2 mtdparts=atmel_nand:1M(bootloader),3M(kernel),-(rootfs)

bootcmd=nand read.jffs2 0x22000000 0x100000 0x200000; bootm

bootdelay=1

baudrate=115200

ethaddr=00:0c:20:02:0a:5b

ipaddr=192.168.0.200

serverip=192.168.0.102

netmask=255.255.255.0

stdin=serial

stdout=serial

stderr=serial

ethact=macb0

Environment size: 353/131067 bytes

U-Boot>

```

The bootend setting of the U-boot reads the Linux kernel from NAND FLASH at address 0x100000 to SDRAM at address 0x22000000 and start executing the kernel code at the same memory address. The NAND FLASH from 0x400000 and up is used for Linux root file system. The U-boot passes the MTD device partition setting to the Linux kernel via the bootargs environment variable.

## Loading Linux Kernel and root File System

The U-boot boot-loader provides many ways to load Linux kernel and file system into FLASH memory. The loading by Ethernet network is shown here. User can consult U-boot manual for other methods of loading data.

After power on the GESBC-9G20 board, stop the U-boot auto-execution by press any key. The following message should be shown on the terminal console on the host PC connected to the GESBC-9G20 board.

```

RomBOOT

U-Boot 1.3.3 (Jul 19 2008 - 15:50:33)

DRAM: 64 MB

NAND: 256 MiB

In:

serial

serial

Out:

Err:

serial

Net:

macb0

macb0: Starting autonegotiation...

macb0: Autonegotiation timed out (status=0x7849)

macb0: link up, 100Mbps full-duplex (lpa: 0x4de1)

Hit any key to stop autoboot:

U-Boot>

```

The network address and server address must be set before network transfer can take place. The following commands will set the SBC IP address and server IP address,

```

set ipaddr xxx.xxx.xxx

set serverip xxx.xxx.xxx

```

The server IP is the IP address where a TFTP server must be run. To load Linux kernel type in the following command,

```

t 0x22000000 uImage

```

The U-boot will load uImage file from the TFTP server whose IP address is specified by the serverip environment variable.

The NAND FLASH sectors must be erased first before new kernel image can be stored. The following command will erase the NAND FLASH sectors reserved for Linux kernel,

```

nand erase 0x100000 0x200000

```

The use the flowing command to store the kernel image from SDRAM to NAND FLASH,

```

nand write.jffs2 0x22000000 0x100000 0x200000

```

The following commands can be used to load root file system into the FLASH memory,

```

nand erase 0x400000 [available_nand_flash_memory_size]

t 0x21000000 rootfs.img

nand write.jffs2 0x21000000 x0400000 $(filesize)

```

Please be noted that the image is first loaded into the SDRAM and then stored into the FLASH memory. The image size can not exceed the available SDRAM on the board.

After the kernel and root file system have been updated the board can be simply reboot by recycle the power.

# **Chapter 5 – Development Tools**

#### Overview

This chapter provides a brief introduction to development tools that are available for the AT91SAM9G20 System-on-a-Chip processor. The central processing core on the AT91SAM9G20 is a 200 MHz ARM926EJ-S processor. The ARM926EJ-S RISC processing core is supported through various toolsets available from third party suppliers. The typical toolset required for the code development is a compiler, assembler, linker and a source-level code debugger. Code debugging is supported via the on-chip JTAG interface.

## **Linux Development Tool Chain**

The Linux development tool chain is available at Glomation website in the support page. A host PC running Linux operating system is required to run the development tools. This guide assumes user had basic Linux or Unix application development knowledge.

### Host Computer Requirement

The host PC should run Redhead, SuSe, or other Linux distribution, a RS-232 serial port, at least 500MB free disk space, and a terminal program such as minicom.

#### Hardware Connection

A null modem cable is required to connect GESBC-9G20 to the host computer.

## Install Linux Development Tool Chain

The ARM Linux Development Tool chain can be installed in any directory on the host system. The following example uses cross compiler default directory /usr/local/arm as the installing directory for the ARM Linux cross compiler.

1. Login as root and untar the tool chain

```

cd /

tar jxvf /<cross compiler tar file directory>/ Generic-arm_gcc-4.2.3-

glibc-2.3.3.tar.bz2

```

2. Set up the directory path variable

```

export PATH=/usr/local/arm/gcc-4.2.3-glibc-2.3.3/arm-unknown-linux-

gnu/bin:$PATH

```

above command can be included in the shell resource file so it is executed every time you login. For bash shell, a good place to put is in .bashrc in your home directory.

## Compile Linux Kernel

The GESBC-9G20 is shipped with Linux kernel version 2.6.27. The patch for the kernel source tree is available at <a href="http://www.linux4sam.org/twiki/bin/view/Linux4SAM/LinuxKernel">http://www.linux4sam.org/twiki/bin/view/Linux4SAM/LinuxKernel</a>.

### Prepare Linux Kernel source

Obtain the kernel source 2.6.27 from http://www.kernel.org. Untar the Linux kernel,

```

tar xjf linue-2.6.27.bz2

```

Patch the kernel source with patches for Atmel AT91SAM9G20-EK,

```

patch -p1 < /<patch-file-directory-path>/patch_file_name

```

### Configure Linux Kernel

The GESBC-9G20 can use the default configuration file for the Atmel AT91SAM9G20-ek evaluation board.

```

make ARCH=arm CROSS_COMPILE=arm-unknown-linux-gnu-

AT91SAM9G20ek_defconfig

```

If additional configuration is required, executing the following command in the Linux kernel directory,

```

make ARCH=arm CROSS COMPILE=arm-unknown-linux-gnu- menuconfig

```

If problem occurs, make sure the default PATH variable is set to the correct tool chain directory

# Compile Kernel

Once Linux kernel has been configured, it can be compiled using following command<sup>1</sup>,

```

make ARCH=arm CROSS_COMPILE=arm-unknown-linux-gnu- uImage

```

The Linux kernel should compile without error and the image file will be created.

\_

<sup>&</sup>lt;sup>1</sup> The U-boot tool mkimage must be pre-installed in order to make final uImage.

# **Chapter 6 – Troubleshooting**

This chapter provides Troubleshooting information. Search the entries in the Problem column in order to find the item that best describes your situation. Then perform the corrective action in the same row. If the problem persists, contact Glomation.